# Bluetooth 5.0 LE | MESH SoC Datasheet of RF04

# (with 4Mb Flash)

DS-RF04-01

Version 3.3

July 6, 2021 released

http://www.bluexmicro.com

### Table of Contents

| 1    | General description                                                                                                                                                                                          | 4  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2    | Feature list                                                                                                                                                                                                 | 5  |

| 3    | Package                                                                                                                                                                                                      | 7  |

| 3.1  | RF04 QFN 40 pins Package ( 5 mm x 5 mm ) with 4Mb Flash                                                                                                                                                      | 7  |

| 3.2  | IR Reflow Temperature-Time Profile                                                                                                                                                                           |    |

| 3.3  | Application circuit                                                                                                                                                                                          | 10 |

|      | <ul> <li>3.3.1 General application circuit</li> <li>3.3.2 Single-End with DC/DC Bucker available, TX PWR: -3dBm (Max)</li> <li>3.3.3 Differential with DC/DC Bucker available, TX PWR: +2dBm(Max)</li> </ul> | 11 |

|      | 3.3.4 Single-End with DC/DC Bucker available, TX PWR: +4dBm(Max)                                                                                                                                             |    |

| 4    | 3.3.5 Differential with DC/DC Bucker available, TX PWR: +8dBm(Max)<br>System overview                                                                                                                        |    |

|      |                                                                                                                                                                                                              |    |

| 4.1  | Electronical Characteristics                                                                                                                                                                                 |    |

|      | <ul><li>4.1.1 Absolute maximum ratings</li><li>4.1.2 Recommended Operating Conditions</li></ul>                                                                                                              |    |

|      | 4.1.3 Radio Frequency Characteristics                                                                                                                                                                        |    |

| 4.2  | Block diagram                                                                                                                                                                                                |    |

| 4.3  | System blocks                                                                                                                                                                                                |    |

| 4.4  | Function mode                                                                                                                                                                                                | 19 |

| 4.5  | System boot sequence                                                                                                                                                                                         | 20 |

| 4.6  | Power domain                                                                                                                                                                                                 | 20 |

| 5    | Bus architecture                                                                                                                                                                                             |    |

| 6    | Address mapping                                                                                                                                                                                              |    |

| 7    | IO Mux                                                                                                                                                                                                       | 27 |

| 8    | CPU                                                                                                                                                                                                          | 29 |

| 8.1  | General description                                                                                                                                                                                          | 29 |

| 9    | Cache controller                                                                                                                                                                                             | 30 |

| 9.1  | Feature List                                                                                                                                                                                                 | 30 |

| 10   | ADC                                                                                                                                                                                                          | 30 |

| 10.1 | General description                                                                                                                                                                                          | 30 |

| 11   | SPI master                                                                                                                                                                                                   | 31 |

| 11.1 | Feature list                                                                                                                                                                                                 |    |

#### **RF04** Datasheet

| 12   | SPI slave                |

|------|--------------------------|

| 12.1 | Feature list             |

| 13   | UART                     |

| 13.1 | Feature list             |

| 14   | IIC                      |

| 14.1 | Feature list             |

| 15   | Power management         |

| 16   | DC/DC Buck Converter     |

| 17   | LDO                      |

| 18   | 32MHz Crystal Oscillator |

| 19   | 32MHz RC Oscillator      |

| 20   | 32KHz Crystal Oscillator |

| 21   | 32KHz RC Oscillator      |

| 22   | PLL                      |

# **1** General description

The RF04 is a System-on-Chip combining an application processor, memories, cryptography engine, power management unit, digital and analog peripherals and a MAC engine complied with Bluetooth<sup>®</sup> Low Energy 5.0 and radio transceiver.

A 32-bit MCU is integrated in RF04 for BLE link layer management and system operation. Rich digital and analog peripheral interfaces are optimized for external control, including GPIO, SPI, UART, IIC, PWM, ADC and LDOS. Power Management Unit with on-chip DCDC buck converter and various Regulators provides ultra-low current consumption for RF04.

# 2 Feature list

- Complies with Bluetooth 5.0 with 1M / 2M bps data rates.

- Radio Transceiver

- -93 dBm RX sensitivity at 1Mbps mode

- -90 dBm RX sensitivity at 2Mbps mode

- RF output power levels: -20dBm, 0dBm, 3dBm and 8dBm

- 50dB RSSI dynamic range

#### Supply Current

- 4.3mA in RX and 4.4mA in TX with On Chip DCDC Converter@4.3V

- 5.5mA in RX and 5.7mA in TX with On Chip DCDC Converter@3.3V

#### Ultralow Current Mode

- Sleep current : 2.5uA ~ 6uA , SRAM ( 16 KB ~ 208 KB ) retention

- Average current: 20uA <sup>1</sup>, during 1.28 sec cycle time (Active / Sleep)

- Notice: Active (Broadcasting ADV) / Sleep (208 KB SRAM retention)

#### Analog Interfaces

- 1 Battery monitoring function from 5.5V to 2.0V

- 2 External channel of ADC (ENOB = 10) with average capability (Oversampling up to ENOB = 12)

- Temperature sensor from -40  $^\circ\!\mathrm{C}$  to 125  $^\circ\!\mathrm{C}$

#### Digital Interfaces

- Up to 14 GPIOs

- 1 Internal Quad-SPI Flash interface

- 1 General SPI interface

- Support both SPIM / SPIS Mode

- 2 UART Flow control up to 1Mbps and supports all the baud rate under 1Mbps, IRDA is supported

- 2 IIC Master / Slave programmable and speed up to 1Mbps

- 2 Timers and 1 Watch-dog Timer

- 5 PWM Outputs

#### Integrated 32-bit MCU

- Clock frequency: 16MHz, 32MHz (Major), 48MHz, 64MHz, 80MHz and 96MHz (Max)

- CPU Benchmarking : 2.07 Coremark / MHz

- SWD debug interface

- AHB / APB bus matrix with speed up to 96MHz

#### Memories

- 128 KB ROM (Boot ROM and BLE stack)

- 512 KB Flash

- 208 KB SRAM

- Composed of 6 pages of 32KB and 1 page of 16KB , with retention capability

- Each 32KB can be set into retention state separately and exchange memory for BLE connection data

- 16KB of 4 way cache controller for external SPI flash which enable CPU run on the external SPI flash, this 16KB cache can be also used as system SRAM when cache is disabled

#### Power Management

- 2.3-5.0V power input

- One 1.2V Integrated DCDC buck converter

- One 1.8V LDO with 40mA output

- Two 3.3V LDO with 50mA & 25mA output each

#### **Cryptographic Engine**

- ECC

- AES-128

#### Package

• QFN40 ( 5 X 5 mm<sup>2</sup> )

#### Operating Temperature

• -25°C to 85°C

# 3 Package

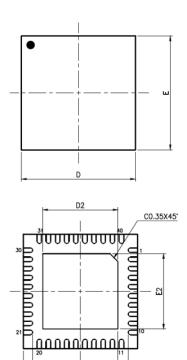

### 3.1 RF04 -- QFN 40 pins Package ( 5 mm x 5 mm ) with 4Mb Flash

| Pin | Symbol    | Туре | Description                           | Pin | Symbol       |     | Туре |

|-----|-----------|------|---------------------------------------|-----|--------------|-----|------|

| 1   | P02       | DIO  | FUNC_IO02/GPIO02                      | 22  | VDD_AWO      |     | РО   |

| 2   | P03       | DIO  | spim0_cs0/SPIS_CS/FUNC_IO01/GPIO03    | 23  | P22          |     | DIO  |

| 3   | P04       | DIO  | spim0_clk/SPIS_CLK/FUNC_IO02/GPIO04   | 24  | P23          | DIC | C    |

| 4   | P05       | DIO  | spim0_miso/SPIS_MISO/FUNC_IO03/GPIO05 | 25  | XTAL32K_P    | AI  |      |

| 5   | P06       | DIO  | spim0_mosi/SPIS_MOSI/FUNC_IO04/GPIO06 | 26  | XTAL32K_N    | AI  |      |

| 6   | P15       | DIO  | FUNC_IO13/GPIO15                      | 27  | VDD_3V_2     | РО  |      |

| 7   | P16       | DIO  | FUNC_IO14/GPIO16                      | 28  | VDD_BAT_2    | PI  |      |

| 8   | P17       | DIO  | FUNC_IO15/GPIO17                      | 29  | VDD_VCO      | PI  |      |

| 9   | P12       | DIO  | FUNC_IO10/GPIO12                      | 30  | LOOP_C       | AIO |      |

| 10  | P13       | DIO  | FUNC_IO11/GPIO13                      | 31  | VDD_CP       | PI  |      |

| 11  | VDD_SRAM  | РО   | VDD_SRAM output                       | 32  | VDD_RF1      | PI  |      |

| 12  | VDD_3V_1  | РО   | Supply to external 3.3V               | 33  | RF_P         | AIO |      |

| 13  | VDD_1V8   | РО   | Supply to external 1.8V               | 34  | RF_N         | AIO |      |

| 14  | VDD_DIG   | PI   | Digital circuit power supply          | 35  | VDD_A        | PI  |      |

| 15  | GND_D     | GND  | Ground for digital circuit            | 36  | VDD_BAT_1    | PI  |      |

| 16  | VDD_1V2   | PO   | DC/DC Converter output                | 37  | P30          | AI  |      |

| 17  | VDD_BAT   | PI   | Battery supply voltage                | 38  | P34          | AI  |      |

| 18  | Ext Reset | DI   | Pull low internally. High active.     | 39  | XTAL32M_P    | AI  |      |

| 19  | P00       | DIO  | swck/GPIO00                           | 40  | XTAL32M_N    | AI  |      |

| 20  | P01       | DIO  | swd/GPIO01                            |     | Cround pad   | CND |      |

| 21  | VDD_CPU   | РО   | VDD_CPU output                        |     | C Ground pad | GND |      |

NOTE: AI : analog input AO : analog output AIO : analog input/output DI : digital input DIO : digital input/output PI : power input PO : power output

L

к

| PKG CODE               | VQFN |                |         |      |  |  |

|------------------------|------|----------------|---------|------|--|--|

| SYMBOLS                | MIN. | NOM.           | MAX.    | UNIT |  |  |

| А                      | 0.80 | 0.85           | 0.90    |      |  |  |

| A1                     | 0.00 | 0.00 0.02 0.05 |         |      |  |  |

| A3                     |      | 0.203 REF      |         |      |  |  |

| В                      | 0.15 | mm             |         |      |  |  |

| D                      |      | 5.00 BSC       |         |      |  |  |

| E                      |      | 5.00 BSC       |         |      |  |  |

| е                      |      | 0.40 BSC       | ,       |      |  |  |

| К                      | 0.20 | -              | -       |      |  |  |

| Lead Frame<br>PAD SIZE |      | 153 X 1        | .5* MIL |      |  |  |

| SYMBOLS                | MIN. | NOM.           | MAX.    | UNIT |  |  |

| D2                     | 3.25 | 3.30           | 3.35    |      |  |  |

| E2                     | 3.25 | 3.30           | 3.35    | mm   |  |  |

| L                      | 0.35 | 0.4            | 0.45    |      |  |  |

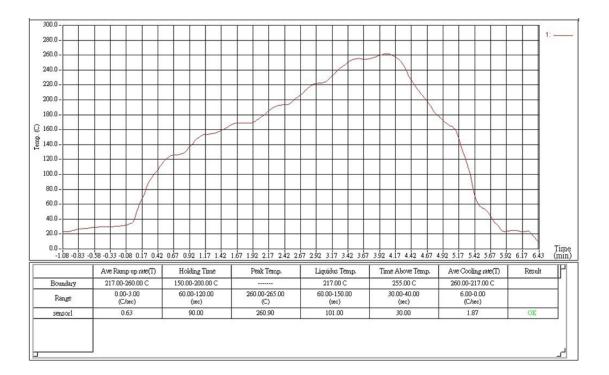

### 3.2 IR Reflow Temperature-Time Profile

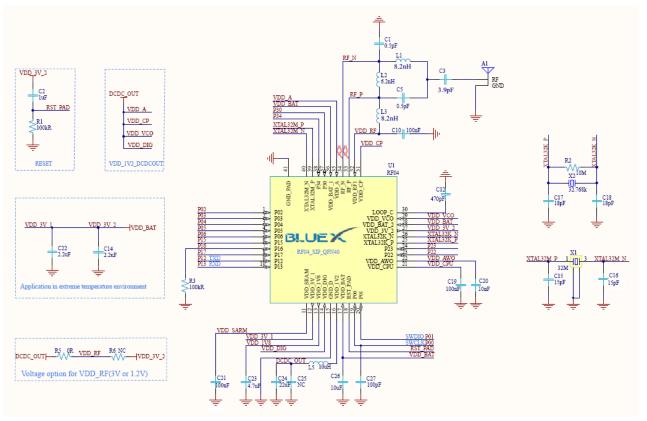

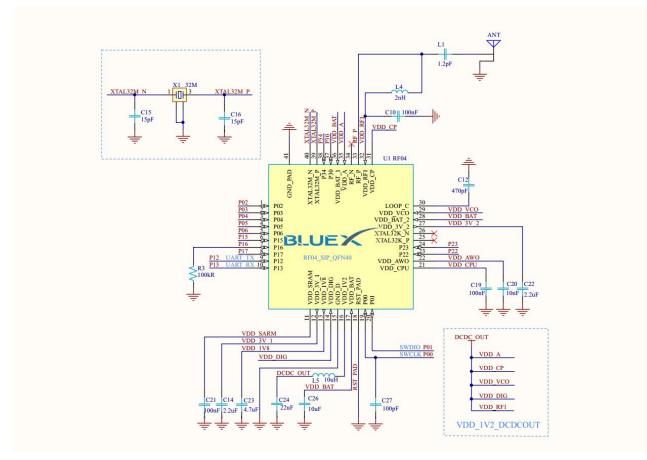

### 3.3 Application circuit

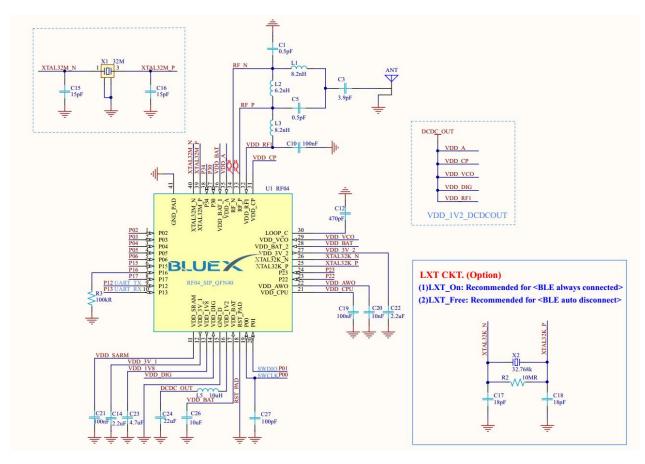

### 3.3.1 General application circuit

| Component          | TX PWR.      | RX SEN.        | LXT    | RF CKT. Structure |  |

|--------------------|--------------|----------------|--------|-------------------|--|

| Standard: 30PCS    | 0 dDm (Max)  | 1Mbps: -93 dBm | Ontion | Differential      |  |

| Option : Add 1 PCS | +8 dBm(Max.) | 2Mbps: -90 dBm | Option | Differential      |  |

**RF04** Datasheet

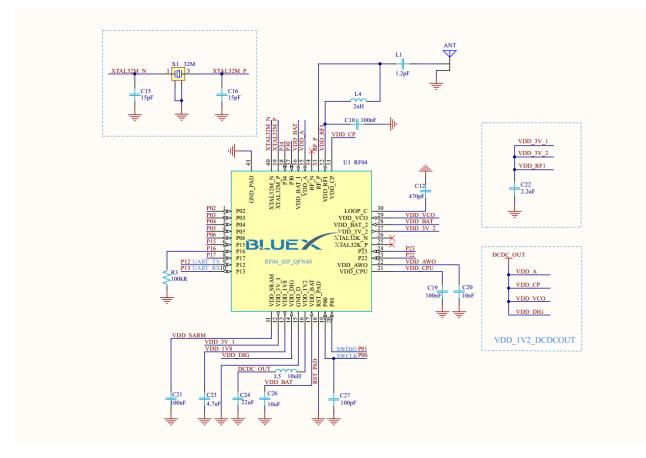

### 3.3.2 Single-End with DC/DC Bucker available, TX PWR: -3dBm (Max)

| Component | TX PWR.      | RX SEN.        | LXT        | RF CKT. Structure |

|-----------|--------------|----------------|------------|-------------------|

| 18 PCS    | -2 dBm(Max.) | 1Mbps: -90 dBm | LXT - free | Single-End        |

| 16 PCS    |              | 2Mbps: -86 dBm | EXT file   | Single Life       |

### 3.3.3 Differential with DC/DC Bucker available, TX PWR: +2dBm(Max)

| Component             | TX PWR.      | RX SEN.        | LXT    | RF CKT. Structure |

|-----------------------|--------------|----------------|--------|-------------------|

| Standard: 26 PCS      | 2 dDm (Max)  | 1Mbps: -93 dBm | Ontion | Differential      |

| Option : Reduce 4 PCS | +2 dBm(Max.) | 2Mbps: -90 dBm | Option | Differential      |

### 3.3.4 Single-End with DC/DC Bucker available, TX PWR: +4dBm(Max)

| Component | TX PWR.      | RX SEN.        | LXT        | RF CKT. Structure |

|-----------|--------------|----------------|------------|-------------------|

| 17 PCS    | +4 dBm(Max.) | 1Mbps: -90 dBm | LXT - free | Single-End        |

| 17 PCS    |              | 2Mbps: -86 dBm | EXT - free | Single-End        |

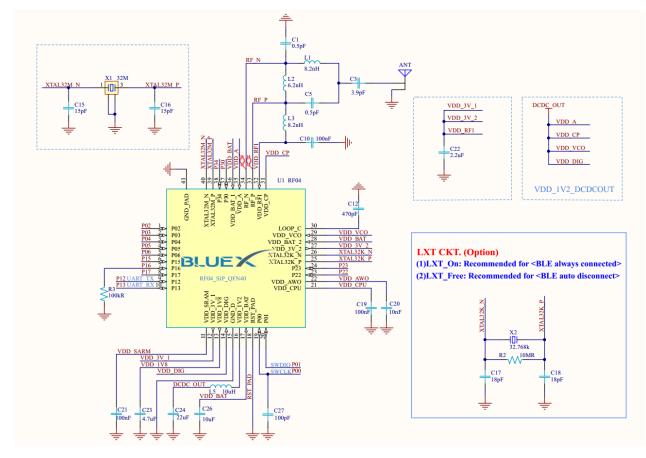

### 3.3.5 Differential with DC/DC Bucker available, TX PWR: +8dBm(Max)

#### Circuit Features

| Component             | TX PWR.       | RX SEN.        | LXT    | RF CKT. Structure |

|-----------------------|---------------|----------------|--------|-------------------|

| Standard: 25 PCS      | 4.9 dBm(Mayr) | 1Mbps: -93 dBm | Ontion | Differential      |

| Option : 4 Reduce PCS | +8 dBm(Max.)  | 2Mbps: -90 dBm | Option | Differential      |

# 4 System overview

### 4.1 Electronical Characteristics

### 4.1.1 Absolute maximum ratings

| Parameters                | Min  | Max  | Unit |

|---------------------------|------|------|------|

| Storage temperature       | -40  | +120 | °C   |

| Voltage applied to inputs | -0.5 | +5.5 | V    |

### 4.1.2 Recommended Operating Conditions

| Parameters                                    | Min                          | Тур | Max          | Units |

|-----------------------------------------------|------------------------------|-----|--------------|-------|

| Ambient Operating Temperature                 | -25                          |     | +85          | °C    |

| Supply Voltage for VDD_BAT                    | 2.3                          | 4.3 | 5.0          | V     |

| Logical high input voltage (for DI type pins) | 0.85 x VDD_IO <sup>(*)</sup> |     | VDD_IO       | V     |

| Logical low input voltage (for DI type pins)  | 0                            |     | 0.2 x VDD_IO | V     |

$Note: VDD_IO$  is programmable as 3.3V or 1.8V individually.

### 4.1.3 Radio Frequency Characteristics

#### TA = 25°C, VDD = 4.3 V, Frequency=2.440 GHz

| Parameter               | Condition                                                 | Min   | Тур | Мах | Unit  |

|-------------------------|-----------------------------------------------------------|-------|-----|-----|-------|

| Dessiver Consitivity    | At 1 Mbps RX Mode, 37 Byte payload length, BER<0.1%.      | -93   |     |     | dBm   |

| Receiver Sensitivity    | At 2 Mbps RX Mode, 37 Byte payload length, BER<0.1%       | -90   |     |     | dBm   |

|                         | Maximum RF Output Power at 0 dBm setting ( Comply with    | -4    | -2  | 0   | dBm   |

|                         | Power Class 3 in Bluetooth Low Energy 5.0 )               | -4    | -2  | 0   | UDIII |

| Transmitter Output Powe | Maximum RF Output Power at 8 dBm setting ( Comply with    | 5 6.5 |     | 8   | dBm   |

|                         | Power Class 1.5 in Bluetooth Low Energy 5.0 )             | D     | 0.5 | 0   | ubiii |

|                         | Receiver with integrated DC/DC Converter                  |       | 4.3 |     | mA    |

|                         | 0 dBm Transmitter with integrated DC/DC Converter         |       | 4.4 |     | mA    |

|                         | 8 dBm Transmitter with integrated DC/DC Converter         |       | 26  |     | mA    |

| Current Consumption     | Sleep with SRAM ( 16KB ~ 208KB ) retention, 32.768KHz     | 2.5   |     | 6   | uA    |

| Current Consumption     | Crystal Clock                                             | 2.5   |     | 0   | uA    |

|                         | Average current during 1.28 sec active (broadcasting ADV) |       | 18  |     | uA    |

|                         | /sleep (SRAM 208 KB retention ) cycle time                |       | 10  |     | uA    |

|                         | CPU Standby with 16MHz Clock running                      |       | 1.5 |     | mA    |

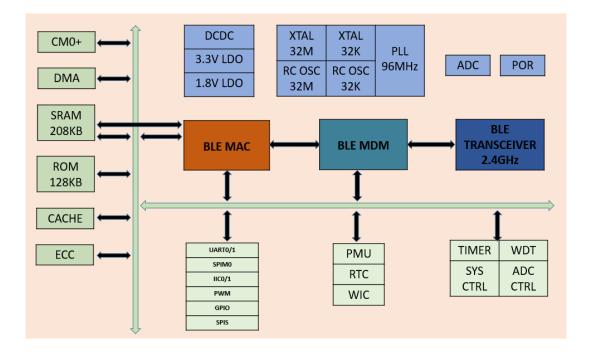

### 4.2 Block diagram

The block diagram of RF04 is shown below.

### 4.3 System blocks

**CPU:** The processor is an entry-level 32-bit processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- A simple architecture that is easy to learn and program.

- Ultra-low power, energy-efficient operation.

- Excellent code density.

- Deterministic, high-performance interrupt handling.

- Platform security robustness, with integrated Memory Protection Unit (MPU).

BLE 5.0 MAC and PHY: This is the BLE MAC and PHY which is compatible with the BLE 5.0 protocol.

BLE RF module: This is the low power RF module which is compatible with the BLE 5.0 protocol.

**Cache Controller:** This is the 32bit 4 way read only cache controller which makes the CPU can run on the external flash with quard-SPI interface. The cache controller offers one cycle latency read access when the read from the CPU hit the cache. If cache miss, the cache controller is responsible to generate the SPI access command and fetch data from the external flash through quard-SPI interface.

**AHB/APB bus matrix:** This is the bus matrix which provides the data access channel between multiple AHB masters and multiple AHB/APB slaves. The access of different master slave pair does not affect each other which improve the data throughput of the system.

**RAM controller:** This is the SRAM controller which converts the AHB bus access to the 208KB SRAM read/write command. Because one of the SRAM is shared with the exchange memory used by the

BLE MAC, the SRAM controller is also responsible for the arbitration between the AHB bus and the BLE MAC.

**ROM controller:** This is the ROM controller which converts the AHB bus access to the 128KB ROM read command. The boot code and the BLE link layer stack are stored in the ROM.

**ROM patch controller:** This is the data patch controller for ROM data. It provides data patching for up to 16 ROM addresses.

**System controller(CPU):** This is the system controller which controls the clock generator, reset generator and the pin share logic of the system. It is also responsible for frequency calibration of the 32KHz clock from RC oscillator.

**DMA controller:** This is the DMA controller which provides directly data access channel between the SRAM and peripheral interfaces. There are 6 DMA channels implemented in the DMA controller.

**ADC controller:** This is the ADC controller which provides the data channel between the ADC and the APB bus. It supports both one time ADC sample and continuous ADC sample. It also supports DMA access by the DMA controller in the continuous sampling mode.

**ECC engine:** This is the ECC codec for the encrypt transmission of BLE. It provides hardware fast ECC calculation which costs less than 50ms for single ECC calculation.

**Pin share controller:** This is the pin share logic which provides flexible pin share scheme for different customers. The pin share logic is controlled by the system controller(CPU).

**Clock generator(CPU):** This is the clock generator which provides clock for all of the modules in the CPU power domain. It implements the clock divider, clock mux/switch and architecture clock gating for the CPU power domain.

**Reset generator(CPU):** This is the reset generator which provides the reset for all of the modules in the CPU power domain. It implements the reset synchronizer and the software reset logic for the CPU power domain.

**UART2AHB:** This is the UART interface module which provides the access channel to all of the system address space for the external UART controller. It can provide the access channel without the help of the CPU which means that even if the CPU does not work correctly, the external UART controller can access all the registers and memory space. It is mainly for debug.

**Timer:** This is the timer counter which is counting in a frequency programmable clock. There are two independent timer counters implemented.

**Watch dog:** This is the watch dog controller for the system, which can work in two modes: system reset mode and interrupt followed by system reset mode. The watch dog can prevent system from entering some dead status by interrupt and reset the system if the system does not kick the watch dog for a long time.

**System controller(PER):** This is the system controller which controls the clock generator, reset generator of the PER power domain.

**Clock generator(PER):** This is the clock generator which provides the clock for all of the modules in the PER power domain. It implements the clock divider, clock mux/switch and architecture clock gating for the PER power domain.

**Reset generator(PER):** This is the reset generator which provides the reset for all of the modules in the PER power domain. It implements the reset synchronizer and the software reset logic for the PER power domain.

**UART interface controller(UART0/UART1):** Asynchronous serial interface controller with throughput up to 2Mbps. UART0 supports flow control and UART1 does not. Both of the UART interface controller support DMA access by DMA controller.

**IIC interface controller(IICO/IIC1):** This is the IIC interface controller which can be programmed to be master or slave. It supports DMA access by DMA controller.

**SPI master interface controller(SPIM0):** This is the SPI master interface with one bit data input and one bit data output and two bit chip select. The maximum throughput is 24Mbps. It supports DMA access by DMA controller.

**SPI slave interface controller(SPIS):** This is the SPI slave interface with one bit data input and one bit data output. The maximum throughput is 6Mbps. It supports DMA access by DMA controller.

**PWM controller:** This is the PWM waveform generator which generates 5 independent PWM output signal. The frequency and the duty cycle of the PWM signal are programmable.

**GPIO controller:** This is the general purpose IO controller which implements 30 GPIOs. The direction and output value are both programmable. And also the interrupt mode is programmable to edge and level.

**Power management unit(PMU):** This is the power management controller of the system which controls the power up and power down flow for each power domain. All of the DCDC/ /LDO are controlled by PMU according to the internal FSM of the PMU.

Wakeup interrupt controller(WIC): The wakeup interrupt controller monitor the wakeup interrupts

and inform the PMU to power up the system if necessary. The wakeup controller also wakeup CPU after the system has been powered up.

**Mode controller:** The mode controller monitor the boot select IO value during the system power up reset active period and inform the CPU from which interface the CPU can get the boot loader and the IO voltage.

Pad ring: All the digital IO cell is implemented in this module.

**Power PWM controller:** This controller is used to control the power output. The power output can be set to on or off. And also the power output can be set to on for some time and off for some time just like a PWM waveform.

Real time controller: This is the real time timer for the system.

**System controller(AWO):** This is the system controller which controls the clock generator, reset generator, power PWM, PMU, pad ring of the AWO power domain. The IO retention function is also implemented in this module.

**Clock generator(AWO):** This is the clock generator which provides all the clock for the AWO power domain and all the other power domain. It implements the clock divider, clock mux/switch and architecture clock gating for the AWO power domain.

**Reset generator(AWO):** This is the reset generator which provides all the reset for the AWO power domain and all the other power domain. It implements the reset synchronizer and the software reset logic for the AWO power domain.

#### 4.4 Function mode

RF04 has two functional modes of operation: Mirrored mode and Cached mode.

In Mirrored mode, the system code is mirrored from the external device to the system SRAM, and CPU is running on the system SRAM. In this mode cache controller is disabled. And the 16KB SRAM used by the cache controller can be used as the normal system SRAM.

In Cached mode, the system code is stored in the external flash, and CPU is running on the external flash. In this mode cache controller is enabled and the 16KB SRAM used by the cache controller can not be used as the normal system SRAM.

Cache mode is used only when the system SRAM is not big enough for system running. Cache mode will cost more power than the mirrored mode and the performance of the CPU in cache mode is

much worse than it is in the mirrored mode.

#### 4.5 System boot sequence

After power up, power up reset will hold low for some time. Then after the power up reset is released, CPU will start to execute code from address 0x0. No address remapping is implemented in RF04 and ROM is always addressed at address 0x0. So after power up the boot sequence in the ROM is executed by CPU.

By default, all of the power sources are powered up after power on reset, and the 32MHz crystal and 32KHz RC oscillator are active. PLL is off by default. 32MHz clock is the main clock source of the system. CPU is working on 32MHz by default.

RF04 can boot from flash interface or UART interface. The IO voltage of the boot interface can be 1.8V or 3.3V. This is decided by two boot select pins. The two boot select pin shall be pulled up or pulled down to predefined value during power on reset period. The value of the boot select pins are latched to the internal boot registers during the power on reset period and be read by the CPU at the beginning of the boot sequence. Then CPU can decide which interface shall boot from and how much is the IO voltage level of the interface by reading the boot registers implemented in the system controller. The clock frequency of flash interface during boot period is 8MHz and the data rate of the UART interface during boot period is 115200bps. If boot from UART then P12 is used as TX data of UART interface and P13 is used as the RX data of UART interface.

The decode logic of the boot select pin is shown below:

P16 is pulled down means boot from flash, P16 is pulled up means boot from UART0(P12/P13). P23 is pulled down means IO voltage is 1.8V, P23 is pulled up means IO voltage is 3.3V. The default IO voltage is 1.8V.

### 4.6 Power domain

The block diagram of the power domain of RF04 is shown below:

| J           |             |           | PER             |             | BLE     |

|-------------|-------------|-----------|-----------------|-------------|---------|

| CPU         | UART2AHB    | DMA       | SPIMO           | RST_GEN_PER | BLE_MA  |

| BUS         | BROM_CTRL   | SRAM_CTRL | SPIS            | GPIO        | BLE_MDI |

| CACHE       | WDOG        | TIMER     | UARTO           | UART1       |         |

| PIN_SHARE   | ADC_CTRL    | ECC       | IICO            | IIC1        | SRAM    |

| ROM_PATCH   | SRAM_MON    | SYSC_CPU  | SYSC_PER        | CLK_GEN_PER | SRAMO   |

| CLK_GEN_CPU | RST_GEN_CPU |           |                 |             | SRAM1   |

| ANALOG&RF   |             |           |                 |             | SRAM2   |

| DCDC        | LDO         | AWO       |                 |             | SRAM3   |

| BLE TX/RX   | POR         | RTC       | PMU             | WIC         | SRAM4   |

| PLL         | 32M RC/XTAL | BLE_LP    | P EXT_INTR      | SYSC_AWO    | SRAM5   |

| 32K RC/XTAL | ADC         | CLK_GEN_A | AWO RST_GEN_AWO | PAD_RING    | SRAM6   |

RF04 is composed of 6 power domains which are CPU, PER, BLE, AWO, SRAM and ANALOG.

ANALOG power domain includes all of the analog and RF submodules and each analog and RF submodule is a dedicated sub power domain and can be powered on/off separately.

The SRAM power domain includes all of the 208kB system SRAM and is divided into 7 SRAM blocks. The size of each SRAM block is 32kB except the last block which is 16kB. Each of the 7 SRAM blocks is a dedicated sub power domain and can be powered on/off separately. The address mapping for the 7 SRAM blocks is shown below:

|       | start address | end address |

|-------|---------------|-------------|

| SRAMO | 0x100000      | 0x107FFF    |

| SRAM1 | 0x108000      | 0x10FFFF    |

| SRAM2 | 0x110000      | 0x107FFF    |

| SRAM3 | 0x118000      | Ox11FFFF    |

| SRAM4 | 0x120000      | 0x127FFF    |

| SRAM5 | 0x128000      | 0x12FFFF    |

| SRAM6 | 0x130000      | 0x133FFF    |

The PER power domain includes all of the digital peripheral interface modules. The PER power domain can work under 0.9V or 1.1V. The PER power domain can be powered off.

The BLE power domain includes BLE MAC and BLE PHY. The BLE power domain can work under 0.9V or 1.1V. The BLE power domain can be powered off.

The CPU power domain includes the core system which includes CPU, DMA, SRAM controller, bus matrix, cache controller, ECC module, system timer and system watch dog. CPU power domain can work under 0.9V or 1.1V. The CPU power domain can be powered off.

The AWO power domain includes the power management module, the IO ring, and the logic which can wake up system from sleep status which includes RTC, BLE low power counter, external interrupt controller. The AWO power domain can not be powered off. AWO power can only work under 0.9V.

All of the other power domains except the AWO and ANALOG power domain work under the same voltage in active mode. Under inactive mode (retention mode) the voltage of SRAM can be programmed to be less than 0.9V to save leakage power of SRAM. Each of the BLE/PER/SRAM\* power domains can be powered off independently. And if CPU is powered off, BLE and PER must be powered off and SRAM\* must be powered off or be set to retention status. The power on and power off sequence is controlled by hardware FSM and triggered by software.

| power  |                                      | AW |     |     |     | SRA | ANAL |

|--------|--------------------------------------|----|-----|-----|-----|-----|------|

| mode   | description                          | 0  | CPU | PER | BLE | М   | OG   |

|        | AWO is working                       |    |     |     |     |     |      |

|        | CPU is working. The working          |    |     |     |     |     |      |

|        | frequency of CPU is more than        |    |     |     |     |     |      |

|        | 32MHz, and CPU is working under      |    |     |     |     |     |      |

|        | 1.1V                                 |    |     |     |     |     |      |

|        | at least one of the SRAM is          |    |     |     |     |     |      |

|        | working(power on)                    |    |     |     |     |     |      |

|        | all of the other power domain is     |    |     |     |     |     |      |

| ACTIVE | on/off programmable by CPU           | ON | ON  | Р   | Р   | Р   | Р    |

|        | AWO is working                       |    |     |     |     |     |      |

|        | CPU is working. The working          |    |     |     |     |     |      |

|        | frequency of CPU is equal to or less |    |     |     |     |     |      |

|        | than 32MHz, and CPU is working       |    |     |     |     |     |      |

|        | under 0.9V                           |    |     |     |     |     |      |

|        | at least one of the SRAM is          |    |     |     |     |     |      |

|        | working(power on)                    |    |     |     |     |     |      |

| ACTIVE | all of the other power domain is     |    |     |     |     |     |      |

| LOW    | on/off programmable by CPU           | ON | ON  | Р   | Р   | Р   | Р    |

|        | AWO is working                       |    |     |     |     |     |      |

|        | CPU is clock gated and the working   |    |     |     |     |     |      |

|        | voltage of CPU is 1.1V               |    |     |     |     |     |      |

|        | at least one of the SRAM is          |    |     |     |     |     |      |

|        | working(power on)                    |    |     |     |     |     |      |

|        | all the other power domain is        |    |     |     |     |     |      |

| SLEEP  | on/off programmable by CPU           | ON | ON  | Р   | Р   | Р   | Р    |

RF04 has 6 power modes which are described in the table below:

| power     |                                    | AW |     |     |     | SRA  | ANAL |

|-----------|------------------------------------|----|-----|-----|-----|------|------|

| mode      | description                        | 0  | CPU | PER | BLE | М    | OG   |

|           | AWO is working                     |    |     |     |     |      |      |

|           | CPU is clock gated and the working |    |     |     |     |      |      |

|           | voltage of CPU is 0.9V             |    |     |     |     |      |      |

|           | at least one of the SRAM is        |    |     |     |     |      |      |

|           | working(power on)                  |    |     |     |     |      |      |

| SLEEP     | all the other power domain is      |    |     |     |     |      |      |

| LOW       | on/off programmable by CPU         | ON | ON  | Р   | Р   | Р    | Р    |

|           | AWO is working under 32KHz         |    |     |     |     |      |      |

|           | CPU, PER and BLE are powered off   |    |     |     |     |      |      |

|           | At least one of the SRAM is in     |    |     |     |     |      |      |

| EXTEND    | retention state                    |    |     |     |     |      |      |

| ED        | All of the other power domain is   |    |     |     |     | ON/O |      |

| SLEEP     | power off                          | ON | OFF | OFF | OFF | FF   | OFF  |

|           | PD_AWO is working under 32KHz      |    |     |     |     |      |      |

|           | CPU, PER and BLE are powered off   |    |     |     |     |      |      |

|           | All of the SRAM are off            |    |     |     |     |      |      |

| DEEP      | All of the other power domain is   |    |     |     |     |      |      |

| SLEEP     | power off                          | ON | OFF | OFF | OFF | OFF  | OFF  |

| Note:     |                                    |    |     |     |     |      |      |

| ON: powe  | r on                               |    |     |     |     |      |      |

| OFF: powe | er off                             |    |     |     |     |      |      |

| P: ON/OF  | F programmable                     |    |     |     |     |      |      |

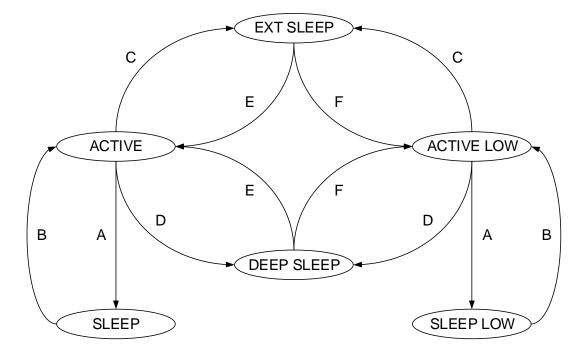

The power state machine of the power states is shown in the block diagram below:

The power state transfer condition in the above diagram is shown in the table below:

| А   | CPU execute WFI with DEEP_SLEEP bit set to low                           |  |  |  |  |  |  |

|-----|--------------------------------------------------------------------------|--|--|--|--|--|--|

| В   | any non-masked interrupt is active                                       |  |  |  |  |  |  |

| С   | CPU execute WFI with DEEP_SLEEP bit set to high, and not all of the      |  |  |  |  |  |  |

|     | active SRAM is powered off together with CPU                             |  |  |  |  |  |  |

| D   | CPU execute WFI with DEEP_SLEEP bit set to high, and all of the active   |  |  |  |  |  |  |

|     | SRAM are powered off together with CPU                                   |  |  |  |  |  |  |

| Е   | Any of the external interrupt, BLE low power interrupt, RTC interrupt is |  |  |  |  |  |  |

|     | active and CPU is waked up with the register VDD_VOLTAGE is set to low   |  |  |  |  |  |  |

|     | which means CPU will work under 1.1V after wake up                       |  |  |  |  |  |  |

| F   | Any of the external interrupt, BLE low power interrupt, RTC interrupt is |  |  |  |  |  |  |

|     | active and CPU is waked up with the register VDD_VOLTAGE is set to       |  |  |  |  |  |  |

|     | high which means CPU will work under 0.9V after wake up                  |  |  |  |  |  |  |

| not | note: register VDD_VOLTAGE is a programmable register in AWO power       |  |  |  |  |  |  |

| don | nain which address is 0x20201048[0]                                      |  |  |  |  |  |  |

|     |                                                                          |  |  |  |  |  |  |

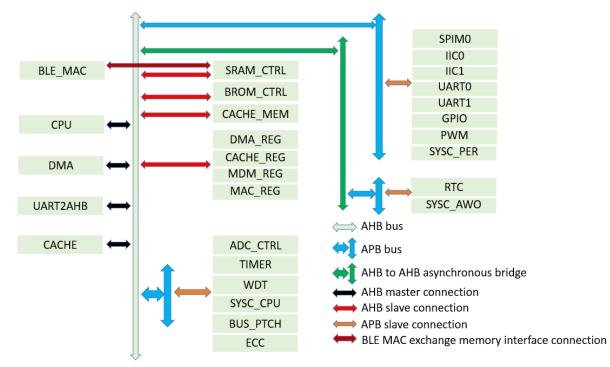

# **5** Bus architecture

The bus architecture of RF04 is shown below.

The system bus is based on AHB and APB. The data width of the bus is 32 bits. The AHB bus works under the same frequency with CPU. The maximum frequency of AHB bus is 96MHz and programmable with 16MHz step. The maximum frequency of APB bus is one half of the frequency

of AHB bus which is 48MHz. The frequency of APB bus is the integer division of the frequency of the AHB bus. There are altogether 4 AHB masters which are CPU, DMA, UART2AHB and CACHE. The exchange memory(EM/32KB) required by the BLE MAC is 32KB and shared with system SRAM. So the BLE MAC can access the SRAM directly through an internal interface. BLE MAC has the highest priority when any other AHB master accesses the same SRAM with BLE MAC at the same time. The accessibility and the priority of the AHB masters to the slaves is shown in the table below:

|          | BROM_CTRL | CACHE_MEM | SRAM_CTRL | OTHER | AWO_REG |

|----------|-----------|-----------|-----------|-------|---------|

| CPU      | 0         | 0         | 1         | 0     | 0       |

| UART2AHB | Х         | Х         | 2         | 1     | 1       |

| DMA      | Х         | Х         | 3         | 2     | Х       |

| CACHE    | Х         | Х         | Х         | Х     | Х       |

| BLE_MAC  | Х         | Х         | 0         | Х     | Х       |

In this table, X means the master can not access the slave. Number means the master can access the slave and 0 has the highest priority. The cache size in the bus diagram is 16kB which is shared with the system SRAM. When cache is enable, the last 16kB system SRAM address space must not be accessed by CPU or other bus master. The last 16kB SRAM is used as the cache SRAM at that time.

The size of the system SRAM is 208kB and the address starts with 0x100000. The system SRAM is composed of 7 sub SRAM blocks as described in chapter 4.5. And if one of the SRAM sub block is not needed any more in the system it can be powered of to save power. BLE\_MAC can only access the fifth SRAM sub block which address starts with 0x128000. When the CPU is running on the external flash, the flash controller must be enabled and the last SRAM sub block is used as the cache and can not accessed by the other AHB master.

# 6 Address mapping

The address mapping of RF04 is shown below:

| addr zone  |          |             | start      | end        | space |

|------------|----------|-------------|------------|------------|-------|

| brom       | brom     |             |            | 0x0001FFFF | 128kB |

| reserved   | reserved |             |            | 0x000FFFFF | 896kB |

| sram       | sram     |             |            | 0x00133FFF | 208kB |

| reserved   |          |             | 0x00134000 | 0x001FFFFF | 816kB |

| reserved   |          |             | 0x00200000 | 0x007FFFFF | 6MB   |

| cache      |          |             | 0x00800000 | 0x00FFFFFF | 8MB   |

| reserved   |          |             | 0x01000000 | 0x1FFFFFFF | 496MB |

| reserved   |          | _           | 0x20000000 | 0x200FFFFF | 1MB   |

|            |          | ble_mac_reg | 0x20100000 | 0x2010FFFF | 64kB  |

|            |          | ble_mdm_reg | 0x20110000 | 0x2011FFFF | 64kB  |

|            | ahb      | dma_reg     | 0x20120000 | 0x20120FFF | 4kB   |

|            |          | cache_reg   | 0x20121000 | 0x20121FFF | 4kB   |

|            |          | reserved    | 0x20122000 | 0x2012FFFF | 56kB  |

|            |          | timer       | 0x20130000 | 0x20130FFF | 4kB   |

|            | apb0     | wdt         | 0x20131000 | 0x20131FFF | 4kB   |

|            |          | sysc_bus    | 0x20132000 | 0x20132FFF | 4kB   |

|            |          | bus_ptch    | 0x20133000 | 0x20133FFF | 4kB   |

|            |          | есс         | 0x20134000 | 0x20134FFF | 4kB   |

|            |          | reserved    | 0x20135000 | 0x20135FFF | 4kB   |

| peripheral |          | adc_ctrl    | 0x20136000 | 0x20136FFF | 4kB   |

|            |          | reserved    | 0x20137000 | 0x2013FFFF | 36kB  |

|            |          | spim0       | 0x20140000 | 0x20140FFF | 4kB   |

|            |          | spis        | 0x20142000 | 0x20142FFF | 4kB   |

|            |          | uart0       | 0x20143000 | 0x20143FFF | 4kB   |

|            |          | uart1       | 0x20144000 | 0x20144FFF | 4kB   |

|            | apb3     | iic0        | 0x20145000 | 0x20145FFF | 4kB   |

|            | apus     | iic1        | 0x20146000 | 0x20146FFF | 4kB   |

|            |          | pwm         | 0x20147000 | 0x20147FFF | 4kB   |

|            |          | gpio        | 0x20148000 | 0x20148FFF | 4kB   |

|            |          | sysc_per    | 0x20149000 | 0x20149FFF | 4kB   |

|            | reserved |             | 0x2014A000 | 0x2014FFFF | 24kB  |

| reserved   |          |             | 0x20150000 | 0x200FFFFF | 704kB |

| awo        | apb1     | rtc         | 0x20200000 | 0x20200FFF | 4kB   |

|            |          | sysc_awo    | 0x20201000 | 0x20201FFF | 4kB   |

# 7 IO Mux

#### The IO mux table of RF04 is shown below.

| pad  |    | func0        |    |            | func | 1            |                | func2 | 2                 |             | func | 3              | f           | unc4 |         |

|------|----|--------------|----|------------|------|--------------|----------------|-------|-------------------|-------------|------|----------------|-------------|------|---------|

| name | 10 | sig_name     | io | sig_name   | io   | en           | sig_name       | io    | en                | sig_name    | io   | en             | sig_name    | io   | en      |

| P00  | В  | swck         | I  | gpio[0]    | В    | gpio00_en    |                |       |                   |             |      |                |             |      |         |

| P01  | В  | swd          | В  | gpio[1]    | В    | gpio01_en    |                |       |                   |             |      |                |             |      |         |

| P02  | В  | gpio[2]      | В  | spim0_cs1  | 0    | spim0_cs1_en |                |       |                   | func_io[0]  | В    | func_io_en[0]  |             |      |         |

| P03  | В  | gpio[3]      | В  | spim0_cs0  | 0    | spim0_en     | spis_cs        | Ι     | spis_en           | func_io[1]  | В    | func_io_en[1]  |             |      |         |

| P04  | В  | gpio[4]      | В  | spim0_clk  | 0    | spim0_en     | spis_clk       | Ι     | spis_en           | func_io[2]  | В    | func_io_en[2]  |             |      |         |

| P05  | В  | gpio[5]      | В  | spim0_miso | Ι    | spim0_en     | spis_miso      | 0     | spis_en           | func_io[3]  | В    | func_io_en[3]  |             |      |         |

| P06  | В  | gpio[6]      | В  | spim0_mosi | 0    | spim0_en     | spis_mosi      | Ι     | spis_en           | func_io[4]  | В    | func_io_en[4]  |             |      |         |

| P12  | В  | uart2ahb_txd | 0  | gpio[12]   | В    | gpio14_en    | ble_mac_dbg[5] | 0     | ble_mac_dbg_en[5] | func_io[10] | В    | func_io_en[10] | rfif_tx[2]  | Ι    | rfif_en |

| P13  | В  | uart2ahb_rxd | I  | gpio[13]   | В    | gpio15_en    | ble_mac_dbg[6] | 0     | ble_mac_dbg_en[6] | func_io[11] | В    | func_io_en[11] | rfif_tx[3]  | I    | rfif_en |

| P15  | В  | gpio[15]     | В  |            |      |              |                |       |                   | func_io[13] | В    | func_io_en[13] | rfif_tx[5]  | I    | rfif_en |

| P16  | В  | gpio[16]     | В  |            |      |              |                |       |                   | func_io[14] | В    | func_io_en[14] |             |      |         |

| P17  | В  | gpio[17]     | В  |            |      |              |                |       |                   | func_io[15] | В    | func_io_en[15] | rfif_tx[6]  | I    | rfif_en |

| P22  | В  | gpio[22]     | В  |            |      |              |                |       |                   | func_io[20] | В    | func_io_en[20] | rfif_tx[11] | I    | rfif_en |

| P23  | В  | gpio[23]     | В  |            |      |              |                |       |                   | func_io[21] | В    | func_io_en[21] |             |      |         |

The programmable registers for the enable signals are listed below:

| -                 | -              |

|-------------------|----------------|

| 0x20132020[23:16] | ble_mac_dbg_en |

| 0x20132020 [13]   | rfif_en        |

| 0x20132020 [12]   | gpio15_en      |

| 0x20132020 [10]   | gpio01_en      |

| 0x20132020 [9]    | gpio00_en      |

| 0x20132020 [8]    | spis_en        |

| 0x20132020 [5]    | spim0_cs1_en   |

| 0x20132020 [4]    | spim0_en       |

| 0x20132024[21:0]  | func_io_en     |

The func\_io is shared by many interface modules and each bit of the func\_io can be programmed to act as any of the shared function. The share table is listed below:

| signal name | io | idx |

|-------------|----|-----|

| uart0_txd   | 0  | 0   |

| uart0_rxd   | Ι  | 1   |

| uart0_cts   | I  | 2   |

| uart0_rts   | 0  | 3   |

| uart1_txd   | 0  | 4   |

| uart1_rxd   | I  | 5   |

| iic0_scl    | В  | 6   |

| iic0_sda    | В  | 7   |

| iic1_scl    | В  | 8   |

| iic1_sda    | В  | 9   |

| pwm0        | 0  | 10  |

| pwm1        | 0  | 11  |

| pwm2        | 0  | 12  |

| pwm3        | 0  | 13  |

| pwm4        | 0  | 14  |

# 8 CPU

### 8.1 General description

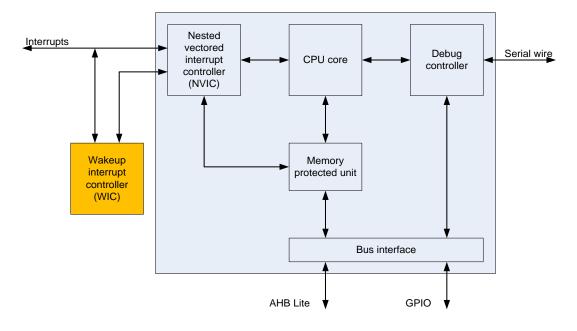

RF04 integrates CPU. The processor is an ultra-low power 32-bit processor designed for a broad range of embedded applications. The block diagram of processor is shown below:

The processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The processor is based on the 16-bit Thumb instruction set and includes Thumb-2 technology. This provides the exceptional performance expected of a modern 32-bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

The processer integrates a nested vectored interrupt controller, a debug controller and a memory protect unit.

# 9 Cache controller

#### 9.1 Feature List

- Zero wait cycle when cache hit

- 8MB cachable address space with the start address programmable

- 16KB cache data size which is shared with the system SRAM

- Supports cache flush command

- 4 Way cache with LRU algorithm

- Read only cache

- 32 bytes cache line size

### **10 ADC**

#### 10.1 General description

The RF04 is equipped with a low power 10-bit general purpose Analog-to-Digital Converter (GPADC). It can operate in unipolar (single ended) mode as well as in bipolar (differential) mode. The ADC has its own voltage regulators (LDO) of 3V. The full scale reference voltage of GPADC is optional set from 2.2V to 2.8V.

#### Features

- 10-bit dynamic ADC with average capability

- Maximum sampling rate 2 Msample/s at 96MHz ADC clock

- Single-ended as well as differential input with two input scales

- Six single-ended or two differential external input channels

- Oversampling up to 64 steps providing effectively up to 12 bits resolution

- Support battery monitoring function from 2.0V to 5.5V

- Support temperature Sensing function from -40 to 125 degree

- DMA support

# 11 SPI master

### 11.1 Feature list

- APB interface with 32 bit data bus

- Supports 1wire mode, one wire of TX data and one wire of RX data

- Supports DMA interface

- 32 words RX and TX data FIFO

- Programmable SPI interface clock, maximum frequency is 24MHz

- Compliant with Motorola SPI interface

- Programmable SPI data size: 4 bits to 32 bits

- SPI mode programmable(phase and clock edge)

- Two chip select output

- Programmable RX data sample edge

# 12 SPI slave

### 12.1 Feature list

- APB interface with 32 bit data bus

- Supports 1wire mode, one wire of TX data and one wire of RX data

- Supports DMA interface

- 32 words RX and TX data FIFO

- Programmable SPI interface clock, maximum frequency is 2MHz

- Compliant with Motorola SPI interface

- Programmable SPI data size: 4 bits to 32 bits

- SPI mode programmable(phase and clock edge)

- Programmable RX data sample edge

# **13 UART**

### 13.1 Feature list

- 32 bytes transmit and receive FIFO

- Hardware flow control(UART0 only)

- IRDA 1.0 SIR mode support(UART0 only)

- Programmable baud rate

- Programmable frame format of data bits per frame

- Optional parity bit and programmable number of stop bits

- DMA transmission

# 14 IIC

### 14.1 Feature list

- Two-wire IIC serial interface consists of a serial data line (SDA) and a serial clock (SCL)

- Three speeds are supported: Standard mode (0 to 100Kbps); Fast mode (400Kbps) or High-speed mode (3.4Mbps)

- Master OR slave IIC operation

- 7- or 10-bit addressing

- 7- or 10-bit combined format transfers

- Transmit and receive FIFO

- Handles Bit and Byte waiting at all bus speeds

- Supports DMA transfer

- Programmable SDA hold time

# **15 Power management**

The power management unit (PMU) in RF04 comprises a DC-DC Buck Converter, various LDOs for the different power domains of the system. The PMU is capable of supplying external devices even during RF04 in sleep mode.

#### Features

- DC-DC Buck Converter with excellent 93% efficiency

- Programmable DC-DC converter output charging sequence

- One LDO output up to 3.3 V with up to 50 mA load capability

- DC-DC converter automatically on/off control during in sleep mode

- Active and Sleep mode current limited LDOs

- Use of small external components

- Supply of external rails (V33, VDD1V8) while in Sleep mode

# **16 DC/DC Buck Converter**

Two DC/DC Buck Converter modes are designed for RF04. One is DC/DC Converter ON and the other is DC/DC Converter Bypass. RF04 will automatically enter DC/DC Converter ON mode within 150 us while CPU is active. And DC/DC Converter will be bypass mode during CPU in sleep mode.

| Item               | Parameter         | Conditions         | MIN. | TYP.  | MAX. | Unit |

|--------------------|-------------------|--------------------|------|-------|------|------|

|                    | Input Voltage     |                    | 2.3  |       | 4.75 | V    |

|                    |                   |                    |      | 1.4   |      | V    |

|                    |                   | DC/DC Converter On |      | 1.3   |      | V    |

|                    | Output Voltage    | ( Default 1.4V )   |      | 1.2   |      | V    |

| DC/DC<br>Converter |                   |                    |      | 1.1   |      | V    |

| converter          |                   | DC/DC Converter    |      | VBAT- |      | V    |

|                    |                   | Bypass             |      | 0.3   |      | v    |

|                    | Quiescent Current | DC/DC Converter On |      | 100   |      | uA   |

|                    | Start-up Time     | DC/DC Converter On |      | 120   |      | usec |

( Ta = -40  $^{\circ}\text{C}$  ~ +85  $^{\circ}\text{C}$  , ~ 2.3V  $~\leq~$  VBAT  $\leq~$  5V )

34 © BlueX Microelectronics Confidential. All Rights Reserved.

# 17 LDO

RF04 provides several LDOs to external power supply, including two 3.3V LDO and one 1.8V LDO. The LDO for external use can be configured as active even in sleep mode. The LDO characteristics are listed below.

| Item     | Parameter                      | MIN. | TYP. | MAX. | Unit |

|----------|--------------------------------|------|------|------|------|

|          | Output Current                 |      |      | 40   | mA   |

| 1.8V LDO | Output Voltage at 96MHz > 10mA |      | 1.8  |      | v    |

( Ta = -40°C ~ +105°C ,  $2.3V \leq VBAT \leq 5.0V$  )

| Item       | Parameter      | MIN. | TYP. | MAX. | Unit |

|------------|----------------|------|------|------|------|

| 3.0V LDO_1 | Output Current |      |      | 25   | mA   |

|            | Output Voltage |      | 3.0  |      | V    |

( Ta = -40°C ~ +105°C ,  $~~2.3V~\leq~VBAT\leq\!\!5.0V$  )

| Item       | Parameter      | MIN. | TYP. | MAX. | Unit |

|------------|----------------|------|------|------|------|

| 3.0V LDO_2 | Output Current |      |      | 50   | mA   |

|            | Output Voltage |      | 3.0  |      | V    |

# 18 32MHz Crystal Oscillator

32MHz Crystal Oscillator characteristics are listed below. Also, frequency compensation, programmable level of frequency compensation capacitors will be implemented to cover 32MHz

Crystal variation, aging ... over temperature range  $-40^{\circ}$ C ~  $+105^{\circ}$ C.

( Ta = -40  $^{\circ}\text{C}$   $\sim$  +105  $^{\circ}\text{C}$  , 2.3V  $\leq$  VBAT  $\leq$  5V )

| Item Parameter           |                            | MIN. | TYP. | MAX. | Unit       |

|--------------------------|----------------------------|------|------|------|------------|

|                          | Oscillation frequency      |      | 32   |      | MHz        |

|                          | Frequency offset           | -20  |      | 20   | ppm        |

| 32MHz Crystal Oscillator | Startup time               |      |      | 150  | μs         |

|                          | Shunt Capacitor ( with NDK |      |      | 10   | ~ <b>Г</b> |

|                          | NX3225SA )                 |      |      | 10   | pF         |

# 19 32MHz RC Oscillator

32MHz RC Oscillator characteristics are listed below.

(Ta = -40°C $\sim$ +105°C, 2.3V  $\leq$  VBAT  $\leq$  5V)

| Item              | Parameter             | MIN. | TYP. | MAX. | Unit |

|-------------------|-----------------------|------|------|------|------|

| Internal 32MHz RC | Oscillation frequency |      | 32   |      | MHz  |

| Oscillator        | Startup time          |      | -    | 20   | μs   |

# 20 32KHz Crystal Oscillator

#### 32KHz Crystal Oscillator characteristics are listed below.

( Ta = -40°C ~ +105°C ,  $2.3V \leq VBAT \leq 5V$  )

| Item                               | Parameter             | MIN. | TYP.   | MAX. | Unit |

|------------------------------------|-----------------------|------|--------|------|------|

| 32.768KHz<br>Crystal<br>Oscillator | Oscillation frequency |      | 32.768 |      | KHz  |

|                                    | Frequency offset      | -20  |        | 20   | ppm  |

|                                    | Series Resistor       |      | 10     |      | MΩ   |

|                                    | Shunt Capacitor       |      | 33     |      | pF   |

# 21 32KHz RC Oscillator

#### 32KHz RC Oscillator characteristics are listed below

( Ta = -40°C ~ +105°C ,  $2.3V \leq VBAT \leq 5V$  )

| Item       | Parameter                         | MIN. | TYP. | MAX. | Unit |

|------------|-----------------------------------|------|------|------|------|

|            | Oscillation frequency             |      | 32   |      | KHz  |

| Internal   | Frequency offset after calibrated | -500 |      | 500  | ppm  |

| 32KHz RC   | by 32MHz Crystal Oscillator       |      |      |      |      |

| Oscillator | Chip-to-chip Variation from -40°C | 10   | -    | 100  | KHz  |

|            | ~+85℃,2.3V~5V                     |      |      |      |      |

# 22 PLL

RF04 provides alternative 96/80/64/48/32/16 MHz system clock. Changing this system's clock can be done within 300 us without affecting the operation of the chip. This PLL dissipates additional 0.4 mA when operating at 96 MHz.

| ltem | Parameter                      | MIN. | TYP. | MAX. | Unit |

|------|--------------------------------|------|------|------|------|

|      | Output Clock ( Default 96MHz ) |      | 96   |      | MHz  |

|      |                                |      | 80   |      | MHz  |

|      |                                |      | 64   |      | MHz  |

|      |                                |      | 48   |      | MHz  |

| PLL  |                                |      | 32   |      | MHz  |

|      |                                |      | 16   |      | MHz  |

|      | Reference Clock                |      | 16   |      | MHz  |

|      | Stable time                    |      |      | 300  | μs   |

$(Ta = -40^{\circ}C \sim +105^{\circ}C, 2.3V \leq VBAT \leq 5V)$